#### **Application Note**

# METHOD OF IMPLEMENTATION (MOI) FOR IBTA 25+ GBPS SERIAL INTERFACE CABLE TEST

#### **Products:**

- ► R&S<sup>®</sup>ZNA

- ► R&S<sup>®</sup>ZNB

- ► R&S®ZNBT

Curtis Donahue | GFM357 | Version 0e | 03.2021

http://www.rohde-schwarz.com/appnote/GFM357

# Contents

| 1          | Introduction                                                                 | 4   |

|------------|------------------------------------------------------------------------------|-----|

| 1.1        | Glossary                                                                     | 5   |

| 1.1.1      | Definition of MOI terminology                                                | 5   |

| 2          | Required equipment                                                           | 7   |

| 2.1        | For InfiniBand Architecture Specification Volume 2, Release 1.5 (Sept. 2020) | 7   |

| 3          | External References                                                          | 8   |

| 4          | IBTA Defined Test Points                                                     | 9   |

| 4.1        | EDR and HDR Test Points                                                      | 9   |

| 5          | Manual Operation                                                             | 11  |

| 5.1        | Test Preparation                                                             | .11 |

| 5.2        | Recall Setup Files                                                           |     |

| 5.3<br>5.4 | Calibration Recommendations                                                  |     |

| 5.4.1      | Introductions                                                                |     |

| 5.4.1      | VNA S-Parameter Validation                                                   |     |

| 5.4.3      | COM & ERL Validation                                                         |     |

| 6          | Channel Operating Margin (COM) and Effective Return Loss (ERL)               |     |

|            | Matlab Scripts                                                               | 30  |

| 6.1        | Introduction                                                                 | .30 |

| 6.2        | Assumptions                                                                  | .30 |

| 6.3        | Considerations                                                               |     |

| 6.4        | Running Matlab Script                                                        | .32 |

| 7          | Recommended VNA Port Mapping                                                 | 34  |

| 7.1        | Introduction                                                                 | .34 |

| 8          | Literature                                                                   | 47  |

Many thanks to Mr. Curtis Donahue, Senior Manager, Ethernet Technologies (UNH-InterOperability Lab, <u>https://www.iol.unh.edu</u>) for his significant contribution to this application note. By combining his expertise as a neutral party within industry and standards bodies knowledge, we have achieved synergies that will benefit both design and test engineers.

# **1** Introduction

This application note created by the Test and measurement specialist Rohde & Schwarz and the University of New Hampshire Interoperability Laboratory (UNH-IOL) describes methods of implementation (MOI) for precise, fast and error-free compliance testing of high-speed cables and backplanes according to InfiniBand standards (up to rate designator HDR), using vector network analyzers test equipment from Rohde & Schwarz.

The purpose of this document is to provide a step by step guideline on how to perform compliance testing for cable assembly and channel characteristics as defined in the following Infiniband Trade Association (IBTA) serial interface specifications:

| Specification                             |                                 | РНҮ Туре    | Typical Connector Type       |

|-------------------------------------------|---------------------------------|-------------|------------------------------|

| InfiniBand<br>Architecture                | Chapter<br>6.8.8.1              | 104G-IB-EDR | QSFP28                       |

| Specification<br>Volume 2,<br>Release 1.5 | Chapter<br>6.9.3.3              | 200G-IB-HDR | QSFP28, QSFP-DD, OSFP        |

| (Sept. 2020)                              | Annex A7:<br>Chapter<br>1.6.3.3 | 400G-IB-NDR | QSFP112, QSFP-DD112, OSFP112 |

At the time of writing this document, the IBTA NDR specification is under development. Even though it is still in draft form, it is expected that the COM and ERL definitions will be identical to that defined by the IEEE P802.3ck Task Force for the 400GBASE-CR4 Ethernet PHY. This MOI does not further describe cable tests on NDR cable types.

Several industries recognized mechanical interfaces can be used in the implementation of the above listed serial specifications. This document assumes the channel/cable assembly under test utilizes one for the following mechanical definitions as the available Test Point (TP):

- 2.92mm, 2.4mm, 1.85mm connector (or equivalent coaxial connector)

- SFP28

- SFP56

- SFP-DD

- QSFP28

- QSFP56

- QSFP-DD

- OSFP

### 1.1 Glossary

| СОМ   | Channel Operating Margin                |

|-------|-----------------------------------------|

| ERL   | Effective Return Loss                   |

| fb    | Nominal Signaling Rate Value            |

| FEXT  | Far-End Crosstalk Aggressor             |

| ICN   | Integrated Crosstalk Noise              |

| ICMCN | Integrated Common Mode Conversion Noise |

| IFBW  | Intermediate Frequency Bandwidth        |

| ILD   | Insertion Loss Deviation                |

| NEXT  | Near-End Crosstalk Aggressor            |

| VNA   | Vector Network Analyzer                 |

#### 1.1.1 Definition of MOI terminology

#### 1.1.1.1 ERL – Effective Return Loss

ERL is a Figure of Merit which incorporates an aggregate of mismatches within the channel.

Unlike standard Return Loss, which is only a function of Impedance Mismatches within the channel, ERL incorporates return loss with the effects of equalization, as well as transmitter noise and receiver frequency response into a signal-to-noise-like figure of merit.

It is not a parameter that can be individually tuned for or otherwise optimized.

The only way to optimize or improve the "result" is to improve or otherwise enhance the individual mismatches within the channel.

#### 1.1.1.2 COM – Channel Operating Margin

COM is also a Figure of Merit, basically it is the delta (magnitude) between Insertion Loss and Isolation, which can be loosely described as a Signal to Noise Ratio or SNR

The referenced "Isolation" is comparable to crosstalk, in the sense that inter-channel or intra-channel leakage is recorded.

Rohde & Schwarz | Application Note Method of implementation (MOI) for IBTA 25+ Gbps serial interface cable test 5

This leakage has traditionally been described as FEXT (far end crosstalk), NEXT (Near end crosstalk).

By means of a formulaic interpretation:

$$COM = 20 \log \frac{A_{signal}}{A_{noise}}$$

#### 1.1.1.3 ILD – Insertion Loss Deviation

Insertion loss is attenuation versus frequency. For passive circuits or structures, Insertion Loss will increase versus frequency. Ideally, insertion loss will increase monotonically with a straight-line transfer function. In practice insertion loss will have ripple or other flatness deviations.

ILD is a polynomial fit of the measured data, which bounds the non-monotonic deviations.

# **2** Required equipment

# 2.1 For InfiniBand Architecture Specification Volume 2, Release 1.5 (Sept. 2020)

| Description              | Equipment                                                                                                                                                                                                                                      | Quantity                 |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| Network Analyzer         | R&S® ZNB40 Vector Network Analyzer, material number<br>1311.6010.84, 4 ports, 100kHz - 40GHz, 2.92mm<br>connectors<br>or<br>R&S® ZNA26 Vector Network Analyzer, material number<br>1332.4500.24, 4 ports, 10MHz - 26.5GHz, 3.5mm<br>connectors | 1                        |

| RF Cable                 | R&S® ZV-Z193, 50 Ohm, DC to 26.5GHz, 3.5mm(f)-3.5mm(m), flexible, phase stable                                                                                                                                                                 | per port of<br>VNA       |

| Calibration Unit/Kit     | R&S® ZN-Z53 Calibration Unit,<br>100kHz to 26.5GHz, 2 ports, 3.5mm(f)<br>or<br>R&S® ZN-Z52 Calibration Unit,<br>100kHz to 26.5GHz, 4 ports, 3.5mm(f)<br>or<br>R&S® ZN-Z135 Calibration Kit, 50 Ohm,<br>0Hz to 26.5GHz, 3.5mm(f)                | 1                        |

| Test Fixture and adapter | Wilder Technologies – www.wilder-tech.com<br>104G-IB-EDR: QSFP28 – 2.92mm<br>200G-IB-HDR: QSFP28 – 2.92mm<br>or<br>PHY-SI - www.phy-si.com<br>104G-IB-EDR: QSFP28 – 2.92mm<br>200G-IB-HDR: QSFP28 – 2.92mm<br>IBTA specs fixtures out to 26GHz | 2                        |

| 50 Ohm Terminator        | Hirose HRM-601A(52)<br>or<br>XMA 2003-6110-00<br>or<br>P1dB P1TR-SAM-26G2W                                                                                                                                                                     | per open<br>fixture port |

| Software Environment     | Matlab/Matlab Runtime                                                                                                                                                                                                                          |                          |

# **3 External References**

#### Table of Applicable IBTA Conformance Requirements

| InfiniBand Archi<br>Volume 2<br>Release 1.5 | tecture     | Differential<br>insertion loss<br>@ Nyquist | ILD | Differential<br>return loss | Differential<br>to<br>common-<br>mode<br>return loss | Common-<br>mode to<br>common-<br>mode<br>return loss | ICN | ICMCN | СОМ |   | IBTA<br>Reference |

|---------------------------------------------|-------------|---------------------------------------------|-----|-----------------------------|------------------------------------------------------|------------------------------------------------------|-----|-------|-----|---|-------------------|

| Chapter 6.8.8.1                             | 104G-IB-EDR | x                                           | x   | x                           | x                                                    | x                                                    | x   | x     |     |   | See<br>Table 93   |

| Chapter 6.9.3.3                             | 200G-IB-HDR | x                                           | x   | x                           | x                                                    | x                                                    | x   | x     | x   | x | See<br>Table 105  |

# **4 IBTA Defined Test Points**

The following sections, and included diagrams demonstrate, the Test Point (TP) definitions that are found in the respective IBTA chapters covered by this MOI. There can be several test points defined depending on the IBTA PHY technology being tested, but not all are applicable to cable assemblies.

### 4.1 EDR and HDR Test Points

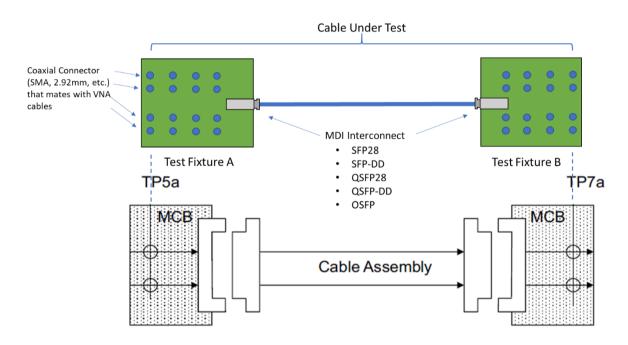

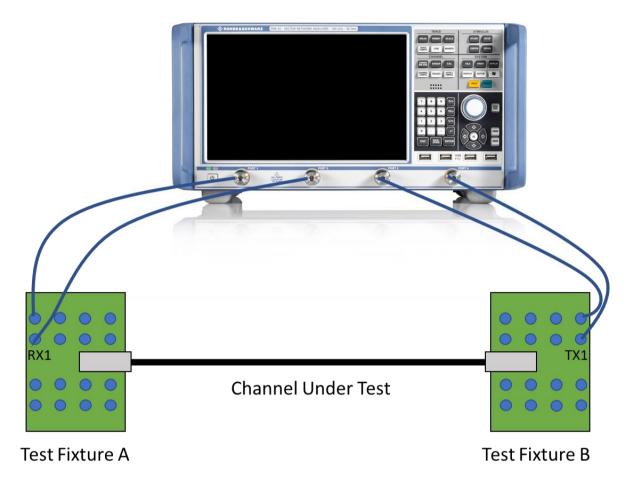

The IBTA test points that are of most interest for the purposes of this MOI are TP5a and TP7a. TP5a and TP7a are where the IBTA channel parameters (differential insertion loss, differential return loss, ERL, etc.) are characterized. Figure 1 demonstrates the relationship between TP5a and TP7a to the cable assembly under test and the test fixtures used to characterize the channel.

Figure 1: Example of IBTA Test Fixtures with Cable Assembly Under Test [5]

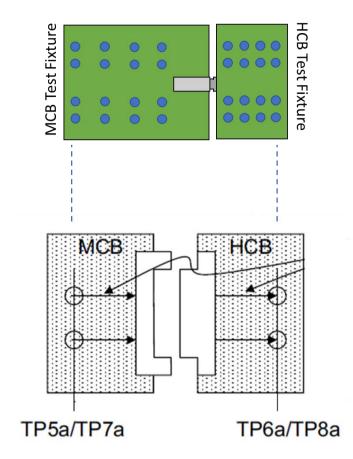

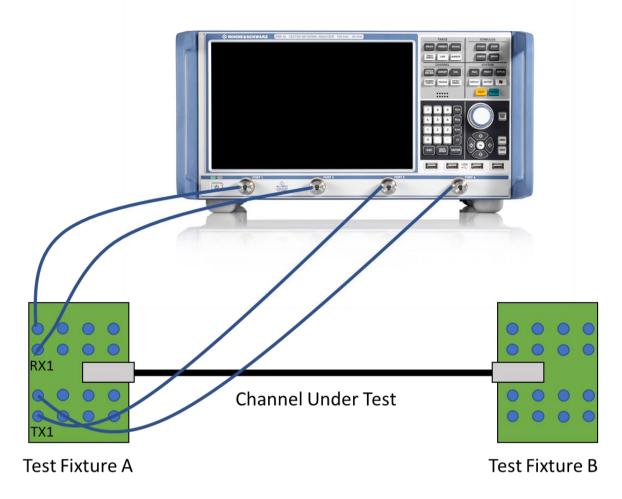

It is worth clarifying that the impairments associated with the MCB test fixture are included in the channel measurements. They are not removed by de-embedding or time gating or any other post-processing calibration method. Instead the IBTA defines additional requirements that determine if a test fixture is sufficient to be used for such applications. Since it is very difficult to accurately isolate the impairments and effects of each side of the MDI interconnect, the IBTA decided to create a "Mated Test Fixture" definition that is measure from TP5a to TP8a across mated HCB and MCB test fixtures. This is shows in Figure 2.

Figure 2: Example of IBTA Mated Text Fixture Set [5]

The mated HCB & MCB parameters, and validation of the conformance of the mated test fixtures, is considered to be outside the scope of this MOI and up to the tester to validate; however, the table below lists the IBTA chapters that include the mated test fixture references.

| Specification             | Cable Definition  |                 |             | IBTA<br>Mated Test<br>Fixture<br>Definition |

|---------------------------|-------------------|-----------------|-------------|---------------------------------------------|

| IBTA Volume 2 Release 1.5 | EDR Linear Cable  | Chapter 6.8.8.1 | 104G-IB-EDR | A1.3                                        |

| (Sept. 2020)              | HDR Linear Cables | Chapter 6.9.3.3 | 200G-IB-HDR |                                             |

As stated previously, impairments associated with the MCB test fixture are included in the channel measurements. They are not removed by de-embedding or time gating or any other post-processing calibration method. However, this can be done for design development purposes using a Rohde & Schwarz ZNA, ZNB, or ZNBT network analyzer. The test fixture used will need to include a '2x Thru' or '1x open' standard to accurately isolate the characteristics of the cable assembly.

# **5 Manual Operation**

This section of the document focuses on how to collect data to perform conformance validation for IBTA channel specifications. A procedure is provided for collecting all necessary S-parameter files, which are used to verify traditional channel metrics such as differential insertion loss and differential return loss, as well calculating the COM and ERL figures of merit. The following sections explain how this conformance analysis is performed without any assisting automation. Currently, the IBTA uses COM and ERL scripts created by the IEEE, only the IEEE 802.3 provided Matlab scripts are considered for validation.

### 5.1 Test Preparation

See the Vector Network Analyzer Settings in the Considerations section of <u>Appendix: Channel Operating</u> Margin (COM) and Effective Return Loss (ERL) Matlab Scripts at the end of this document.

Take care to use the recommended parameters specific to the Infiniband PHY type being tested.

### 5.2 Recall Setup Files

There are recall files delivered together with this document which makes it more convenient to perform the required measurements. There is one recall file for each IBTA specification covered by this MOI.

Recalling the setup files

- 1. First press the green **PRESET** button on the front panel of the instruments

- 2. After that press **FILE** button on the front panel

- 3. Select Open Recall... in 'File' menu

- 4. Open the recall files (\*.znx) for the desired tests. In total there are 3 recall files for the different tests associated with each channel type:

| 1. | IBTA_104G-IB-EDR.znx |

|----|----------------------|

| 2. | IBTA_200G-IB-HDR.znx |

5.

6. Overview about the setting in the different recall files:

| Recall File                                          | Applicable<br>Specification                       | Start     | Stop        | Step<br>size | IFBW | Power |

|------------------------------------------------------|---------------------------------------------------|-----------|-------------|--------------|------|-------|

| ZNA_IBTA_104G-IB-EDR.znx<br>ZNB_IBTA_104G-IB-EDR.znx | *IBTA Volume 2,<br>Release 1.5<br>Chapter 6.8.8.1 | 10<br>MHz | 26<br>GHz   | 5<br>MHz     |      | 0 dBm |

| ZNA_IBTA_200G-IB-HDR.znx<br>ZNB_IBTA_200G-IB-HDR.znx | *IBTA Volume 2,<br>Release 1.5<br>Chapter 6.9.3.3 |           | 26.5<br>GHz | 5<br>MHz     |      | 0 dBm |

\*: At the time of this MOIs creation the IBTA Volume 2 Release 1.5 Specification was still being edited. Recall files for EDR and HDR PHYs are based on the September 2020 release.

Note that instrument state files between the ZNA and ZNB vector network analysis are not interchangeable. When selecting the file appropriate for the PHY type under test, also take care to select to the instrument state file specific to the VNA model being used.

### 5.3 Calibration Recommendations

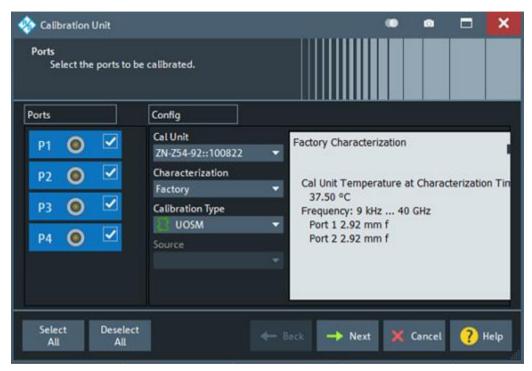

This section described the recommended procedure to calibrating the VNA before collecting the touchstone files needed for processing COM and ERL of a Channel Under Test. The following images are derived from the graphical interface included on a ZNBT40 instrument.

1. While the VNA is powered off, connect all necessary accessories (monitor, keyboard, etc.) including the ZN-Z54 (or applicable) calibration unit.

2. Power on and let the VNA idle for at least 45 minutes. Measurements are very sensitive to changes in temperature, so it is very important that the instrument be running for some time before data is collected, allowing it to acclimate to its internal operating temperature.

- 3. Launch the VNA software interface if it did not open automatically.

- 4. Navigate the graphical interface and press the "Preset" button.

5. Load the appropriate Instrument Configuration file as provided by Rohde & Schwarz for the PHY type to be tested. This is described above in <u>Recall Setup Files</u>

Verify that the following VNA parameters were loaded correctly for the respective PHY under test:

Rohde & Schwarz | Application Note Method of implementation (MOI) for IBTA 25+ Gbps serial interface cable test 12

- Balanced Ports: 1-3, 2-4

- Start Frequency: 10 MHz

- Stop Frequency: The Stop Frequency is specific to the PHY type under test. The values are as follows:

- ► 26 GHz for IBTA EDR PHY types

- ▶ 26.5 GHz for IBTA HDR PHY types

- Frequency spacing: 5 MHz

▶ Intermediate Frequency Bandwidth (IFBW) = 10 KHz

Power: 0 dBm

6. Once sufficient time has lapsed to acclimate the internal temperature of the instrument (see step 2), click the "Cal" button in the software menu.

| Trace             |                 |  |  |  |  |

|-------------------|-----------------|--|--|--|--|

| Meas              | Format          |  |  |  |  |

| Scale             | Trace<br>Config |  |  |  |  |

| Line              | Marker          |  |  |  |  |

| Stim              | ulus            |  |  |  |  |

| Start             | Stop            |  |  |  |  |

| Center            | Span            |  |  |  |  |

| Char              | nnel            |  |  |  |  |

| Channel<br>Config | Sweep           |  |  |  |  |

| Power<br>Bw Avg   | Trigger         |  |  |  |  |

| Cal               | Offset<br>Embed |  |  |  |  |

| Syst              | em              |  |  |  |  |

| File              | Print           |  |  |  |  |

| Display           | Setup           |  |  |  |  |

| Applic            | Preset          |  |  |  |  |

|                   |                 |  |  |  |  |

7. Then click "Start ... (Cal Unit)", from the submenu that appears.

| Cal                   | ×                     | Trace             |                 |  |  |

|-----------------------|-----------------------|-------------------|-----------------|--|--|

|                       |                       | Meas              | Format          |  |  |

| Calibration           | Start                 |                   |                 |  |  |

| Start<br>Auto Cal     | Cal                   | Scale             | Trace<br>Config |  |  |

| Start 🛁               | Cal<br>Devices        | Line              | Marker          |  |  |

| (Cal Unit) 🕌          | Power Cal<br>Settings | Stim              | ulus            |  |  |

| (Manual)              | Use                   | Start             | Stop            |  |  |

| Repeat 😷              | Cal                   |                   |                 |  |  |

|                       |                       | Center            | Span            |  |  |

| Scalar Power Cal      |                       | Channel           |                 |  |  |

| Power<br>Cal          |                       | Channel<br>Config | Sweep           |  |  |

| SMARTerCal            |                       | Power<br>Bw Avg   | Trigger         |  |  |

| Start<br>(Cal Unit) 🚺 |                       | Cal               | Offset<br>Embed |  |  |

| Start<br>(Manual)     |                       | Syst              | em              |  |  |

| Repeat                |                       | File              | Print           |  |  |

| Calibrate All         |                       | Display           | Setup           |  |  |

| Configure<br>+ Start  |                       | Applic            | Preset          |  |  |

8. A new window will appear in the middle of the screen with information specific to the calibration unit being used. Choose the ports you would like to calibrate (typically this is all 4 ports). Make sure the check box next to each applicable port is selected. Additionally, the user may choose the Calibration Type in this window. If using a automated calibration unit, UOSM is the recommended type. Once all settings are confirmed, press "Next".

9. The next window describes the port combinations to be connected to the calibration unit. The default connects Port 1 to all other ports. Press "Start".

| 🚸 Calil     | bration Unit                  |                                |           |                        |       |      |         | ۰ | ۵      |                | ×         |

|-------------|-------------------------------|--------------------------------|-----------|------------------------|-------|------|---------|---|--------|----------------|-----------|

| Conne<br>Se |                               | ections for Calib              | ration U  | nit.                   |       |      |         |   |        |                |           |

| (III) (     | al Type                       | Port                           | s         |                        |       |      |         |   |        |                |           |

| 1 2         | 🖞 UOSM 👘                      | P1, I                          | 2, P3, P4 | 4,                     |       |      |         |   |        |                |           |

|             | al Unit Port 1<br>2.92 mm (f) | Cal Unit Port 2<br>2.92 mm (f) |           |                        |       |      |         |   |        |                |           |

| 1 P         | ort 1 💌                       | Port 2                         |           |                        |       |      |         |   |        |                | 18        |

| 2 P         | ort 1 🔹 🔻                     | Port 3                         |           |                        |       |      |         |   |        |                |           |

| 3 P         | ort 1 🔹 🔻                     | Port 4                         |           |                        |       |      |         |   |        |                |           |

|             | Ī                             | Detect<br>Port Assignme        | nt Po     | Default<br>ort Assignr |       |      |         |   |        |                |           |

|             |                               |                                |           |                        | 🔶 Bad | :k ) | ► Start | × | Cancel | <mark>?</mark> | lelp<br>i |

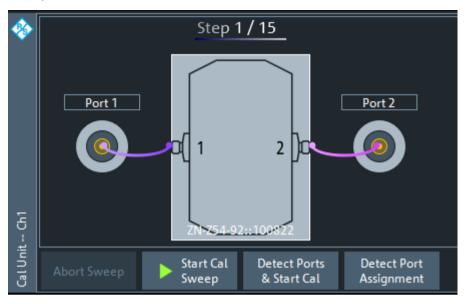

10. Now the graphical interface shows the first port combination to be calibrated. In the bottom left corner of the screen is a diagram of the showing that Port 1 should connect to the left side of the calibration unit, and Port 2 on the right. Once the cables are connected appropriately and sufficiently torqued, click the "Start Cal Sweep" button.

11. Once the sweep for the Port 1 & Port 2 combination is complete, click "Next" in the bottom right corner of the screen.

12. Repeat steps 10 & 11 for the respective port combination specified by the software.

13. Once all port combinations have been calibrated, press the "Save" button in the bottom right corner of the screen.

14. Calibration is complete, and ready to proceed to collecting the necessary touchstone files.

NOTE: Additional calibration, de-embedding, or port extension procedures are not required by the standards covered in this MOI. Instead, the channel conformance parameters specified by the IBTA are designed assuming a test fixture of a specific loss budget is used during testing. The standards bodies go to great lengths to specify requirements regarding the test fixture characterization, and it is the responsibility of the tester to verify that the set of test fixture module compliance boards (MCB) being used during testing meet these requirements. The test fixture requirements can be found in the respective Clause or section of the standard that defines the PHY type under test. Verification of the MCB test fixtures, or additional de-embedding of the fixtures, is considered outside the scope of this MOI.

### 5.4 Compliance Measurements

#### 5.4.1 Introductions

This section defines the test procedures to collect all data necessary to fully characterize a given channel, and validate it to the requirements defined in the respective standards identified in this MOI. This section is divided into two subsections; <u>6.3.2</u> describes the channel parameters that can be verified on the VNA (such as differential insertion loss), and <u>6.3.3</u> describes the process to collect the s4p files necessary to calculate a channels COM and ERL (which requires additional software processing on a PC).

#### 5.4.1.1 Assumed Pin Assignment

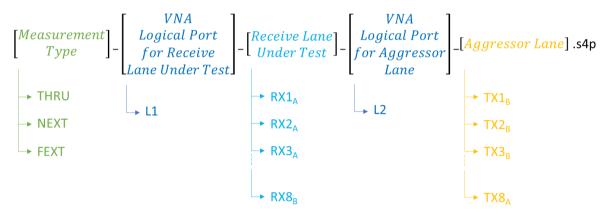

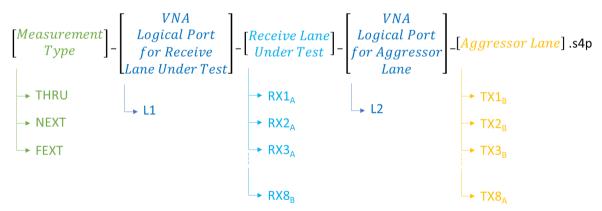

Since several of the PHY types considered in this MOI have multiple transmit lanes, a consistent pin mapping and naming convention is needed to easily describe the test setup and which S-parameter measurements apply to which pins. The following naming convention is recommended,

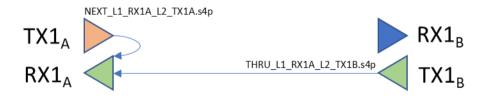

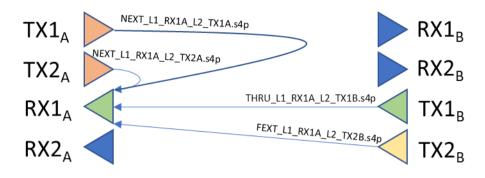

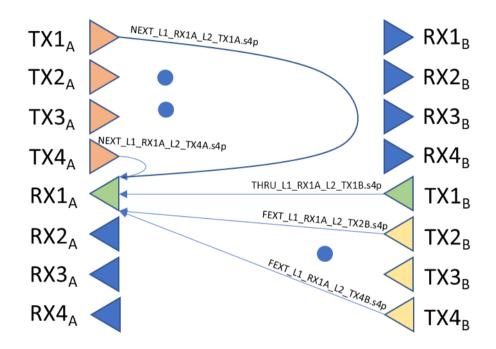

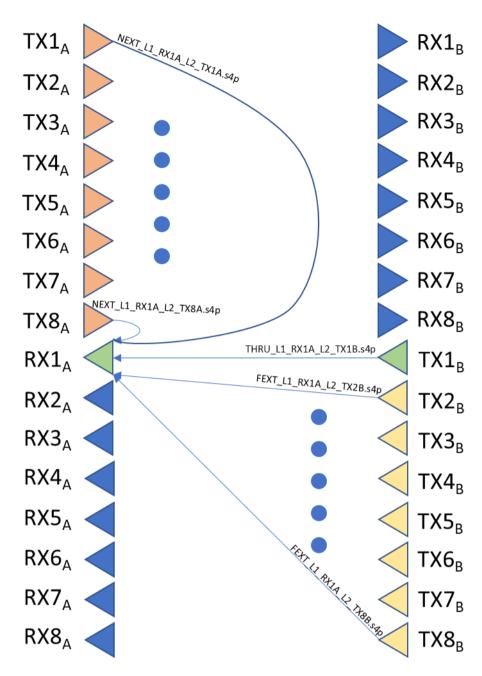

Below are diagrams for each PHY type (1x, 2x, 4x, or 8x transmit lanes) with touchstone file names using the above formula:

Figure 3: PHY with 1x transmit lanes (CR1/KR1 or equivalent) connections for RX1A Victim

Figure 4: PHY with 2x transmit lanes (CR2/KR2 or equivalent) connections for RX1A Victim

Figure 5: PHY with 4x transmit lanes (CR4/KR4 or equivalent) connections for RX1A Victim

Figure 6: PHY with 8x transmit lanes (CR8/KR8 or equivalent) connections for RX1A Victim

#### 5.4.2 VNA S-Parameter Validation

This section defines the procedure to validate the conformance requirements that do not need additional software to process. The exact S-Parameters with corresponding conformance masks and limits are unique to each PHY type under test. The following is a list of parameters covered:

- Differential Insertion Loss SDD21

- ▶ Differential Return Loss SDD11, SDD22

- ► Differential to Common-Mode Return Loss SCD11, SCD22

- Differential to Common-Mode Conversion Loss SCD21

- Common-Mode to Common-Mode Return Loss SCC11, SCC22

- 1. Make sure that the VNA is calibrated as specified above, in <u>Calibration Recommendations</u>.

- 2. Connect the VNA ports to the test fixture interface as follows:

VNA Port 1 to RX1A (+)

VNA Port 3 to RX1A (-)

VNA Port 2 to TX1B (+)

VNA Port 4 to TX1B (-)

For best results, all coaxial connectors for TX and RX lanes that are not connected to the VNA test instrument should be terminated with 50 Ohm loads.

The following procedures assume a 4-lane interface (such as QSFP28) is being tested. This is merely a convenience to the reader, the following instructions apply to all of the interfaces described in <u>Overview</u>.

3. Perform an acquisition of the VNA, collecting the "Thru" measurements of the RX1A lane.

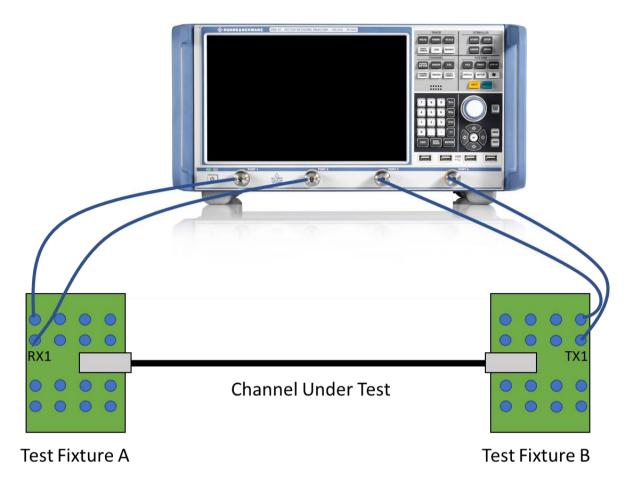

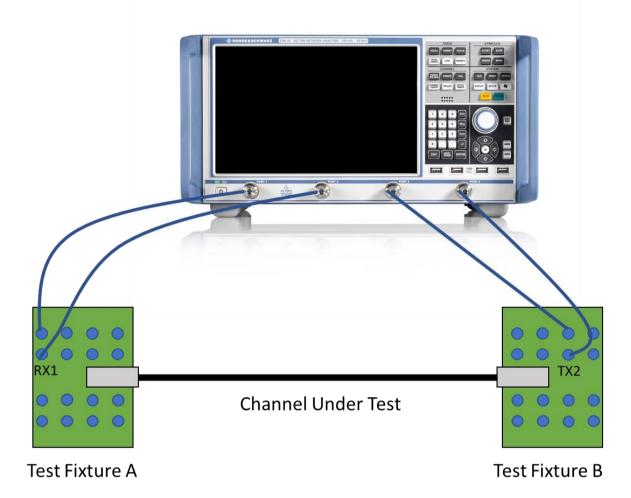

Figure 7: Example QSFP28 setup for RX1A "Thru" measurement

4. Review the individual S-Parameters with associated limit lines in the VNA software interface.

Figure 8: Example of pass and fail indication

- 5. Repeat Step 3-4 for each additional receive lane on Side A of the channel.

- 6. Repeat Step 3-5 for Side B (RX1B, etc.) of the channel.

- 7. Done.

#### 5.4.3 COM & ERL Validation

This section defines the test procedure to collect all data to characterize the COM and ERL.

- 1. Make sure that the VNA is calibrated as specified above, in Calibration Recommendations.

- 2. Connect the VNA ports to the test fixture interface as follows:

VNA Port 1 to RX1A (+)

VNA Port 3 to RX1A (-)

VNA Port 2 to TX1B (+)

VNA Port 4 to TX1B (-)

For best results, all coaxial connectors for TX and RX lanes that are not connected to the VNA test instrument should be terminated with 50 Ohm loads.

The following procedures assume a 4-lane interface (such as QSFP28) is being tested. This is merely a convenience to the reader, the following instructions apply to all of the interfaces described in <u>Overview</u>.

NOTE: The COM/ERL Matlab scripts assume the touchstone files to be processed are measured in a 4-port setup, so the remainder of the procedures in this section will assume that a 4-port setup is being used. If a VNA configuration of >4 ports is used for collecting all necessary data, it is necessary to derive an .S4P equivalent of the touchstone files saved before being able to proceed to Step 6. See <u>Appendix</u>: <u>Recommended VNA Port Mapping</u> for suggested port configuration for ZNB40 and ZNA43.

3. Save all necessary touchstone files for receiver lane RX1A. The following naming convention is recommended:

For example, when collecting the touchstone file which includes the differential insertion loss and differential return loss of receiver RX1A, or the RX1A "Thru" file, the file name would be:

THRU\_L1\_ RX1A\_L2\_TX1B.s4p

A full list of all s4p touchstone file names, following the above convention, is provided in <u>Appendix:</u> <u>Recommended VNA Port Mapping</u>.

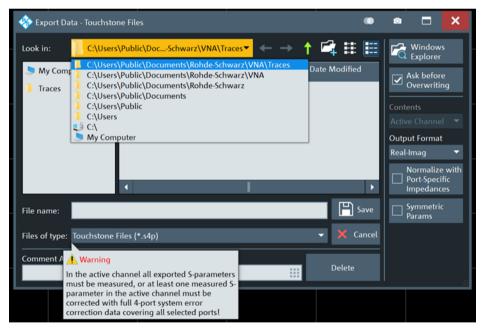

The s4p file can be saved by selecting File > Trace Data > s4p Port 1,2,3,4...

| Svst                   |      |                |   |  |

|------------------------|------|----------------|---|--|

| File                   | DI   |                |   |  |

| Display                | Set  | up             |   |  |

| Applic                 | Pre  |                |   |  |

| File                   |      |                | × |  |

| Import                 |      | Recall<br>Sets |   |  |

| Export snp F           | iles | Favorites      |   |  |

| s1p<br>Active Trace    |      | Print          |   |  |

| s1p<br>Port 1          |      | Trace          |   |  |

| s2p<br>Port 1, 2       |      | Data           |   |  |

| s3p<br>Port 1, 2, 3    | More |                |   |  |

| s4p<br>Port 1, 2, 3, 4 |      |                |   |  |

| snp<br>Free Config     |      |                |   |  |

Lastly, manually enter the name as described above.

a. Collect the "Thru" touchstone. Save as 'THRU\_L1\_ RX1A\_L2\_TX1B.s4p'.

Figure 9: Example QSFP28 setup for RX1A "Thru" measurement

b. Collect the "NEXT" touchstone file(s). Save as 'NEXT\_L1\_ RX1A\_L2\_TX1A.s4p', 'NEXT\_L1\_ RX1A\_L2\_TX2A.s4p', 'NEXT\_L1\_ RX1A\_L2\_TX3A.s4p', and 'NEXT\_L1\_ RX1A\_L2\_TX4A.s4p', respectively.

Figure 10: Example QSFP28 setup for RX1A "NEXT" measurement from TX1A

c. Collect the "FEXT" touchstone file(s). Save as ' FEXT\_L1\_ RX1A\_L2\_TX2B.s4p', 'FEXT\_L1\_ RX1A\_L2\_TX3B.s4p', and 'FEXT\_L1\_ RX1A\_L2\_TX4B.s4p', respectively.

Figure 11: Example QSFP28 setup for RX1A "FEXT" measurement from TX2B

- 4. Repeat Step 3 for each additional receive lane on Side A of the channel.

- 5. Repeat Step 3-4 for Side B (RX1B, etc.) of the channel.

6. Execute the COM/ERL scripts as described in <u>Appendix: IEEE Channel Operating Margin (COM) and</u> <u>Effective Return Loss (ERL) Matlab Scripts</u> with the data collected in Step 3.

- 7. Repeat Step 6 for each receive lane on Side A, as collected in Step 4.

- 8. Repeat Step 6 for each receive lane on Side B, as collected in Step 5.

- 9. Done.

# 6 Channel Operating Margin (COM) and Effective Return Loss (ERL) Matlab Scripts

### 6.1 Introduction

The IEEE 802.3 Working Group adopted COM and ERL as channel metrics for several 25+ Gbps serial interfaces. The underlying post-processing functions of COM and ERL are too extensive and complicated to include within the IEEE 802.3 Standard text, instead the IEEE 802.3 Working Group published Matlab scripts necessary to calculate the COM and ERL conformance values. The scripts were created in Matlab by IEEE 802.3 Working Group participants. Each specification has a unique Matlab script and Excel XLS configuration file that is publicly available for review and use, the Matlab scripts for the IEEE definitions can be found at the respective links below:

- 200G-IB-HDR (<u>IEEE 802.3cd-2018</u>)

- ► 400G-IB-NDR (IEEE P802.3ck Task Force) currently in-development

The IBTA has also adopted COM and ERL for their HDR cable specification, however the HDR COM and ERL files are identical to the IEEE 802.3cd files. IBTA points to the IEEE as an external reference for these requirements.

At the time of writing this document, the IBTA NDR specification is under development. Even though it is still in draft form, it is expected that the COM and ERL definitions will be identical to that defined by the IEEE P802.3ck Task Force for the 400GBASE-CR4 Ethernet PHY.

## 6.2 Assumptions

This document assumes that the reader has successfully downloaded the appropriate COM/ERL scripts for their respective product and has the necessary licenses to run a Matlab environment to process channel measurements. Given that the Matlab environment is setup correctly, the COM/ERL scripts will run without error. Any errors witnessed when running the Matlab scripts are up to the user to resolve and outside the scope of this MOI.

This document also assumes that the user can collect the necessary touchstone files to accurately characterize the COM and ERL of the device under test. The exact procedure for collecting touchstone files on vector network analyzers not explicitly listed in this document is outside the scope of this MOI. Additionally, it is assumed that the test fixtures used for collecting the channel characteristics meets the test fixture requirements of the respective PHY interface being tested. This is up to the tester to verify.

# 6.3 Considerations

To properly run the COM/ERL Matlab scripts for conformance validation, the following needs to be considered:

All lanes in a channel/cable assembly are required to be validated The COM/ERL Matlab scripts are run for each lane in a cable assembly individually. Performing COM analysis on a single lane is not sufficient to validate the conformance of a channel.

Rohde & Schwarz | Application Note Method of implementation (MOI) for IBTA 25+ Gbps serial interface cable test 30

#### COM Configuration XLS File

COM/ERL are figures of merit that are meant to indicate signal quality at the receiver of a Host PHY. To accurately determine the signal quality at the end of a channel, characteristics of the input signal to the channel under test from the transmitter of the link partner PHY need to be known. Complimenting each Matlab script is an xls file that includes default transmitter parameters used for conformance validation. These values can be adjusted for internal development, but the original values (as provided by IEEE 802.3) are required to be used when validating conformance.

#### • COM/ERL is defined in reference to the receiver of a Host device

COM/ERL are figures of merit that are meant to indicate signal quality at the receiver of a Host PHY. As such, all touchstone files need to be measured in reference to a receive lane (ie RX1A, RX2A, etc.). This means that all touchstone files associated with a crosstalk aggressor are to be stimulated at the respective TX aggressor input and observed at the RX victim output under test.

#### Number of Touchstone files

For full conformance validation, the user is required to measure all S-parameters of the victim lane. This results in multiple touchstone files per lane under test. For each lane in a channel/cable assembly, the following is required:

- "Thru" measurement: Touchstone file which includes the differential insertion loss and differential return loss of the lane under test. There is always one "Thru" for each victim lane.

- "NEXT" measurement(s): Touchstone file which includes the S-parameter data associated with near-end crosstalk aggressors in the assembly. The number of NEXT aggressors is dependent on the specific mechanical interface being tested. The number of "NEXT" measurements for each interface is as follows:

- SFP28: One NEXT measurement

- SFP-DD: Two NEXT measurement

- QSFP28: Four NEXT measurement

- QSFP-DD: Eight NEXT measurement

- OSFP: Eight NEXT measurement

- "FEXT" measurement(s): Touchstone file which includes the S-parameter data associated with Farend crosstalk aggressors in the assembly. The number of FEXT aggressors is dependent on the specific mechanical interface being tested. The number of "FEXT" measurements for each interface is as follows:

- SFP28: Zero FEXT measurement

- SFP-DD: One FEXT measurement

- QSFP28: Three FEXT measurement

- QSFP-DD: Seven FEXT measurement

- OSFP: Seven FEXT measurement

- Vector Network Analyzer Settings To accurately validate the COM and ERL of a channel, the following minimum VNA settings need to be applied:

- Start Frequency: 10 MHz or less

- Stop Frequency: fb or higher

- IEEE 802.3bj-2014 & 802.3by-2016 PHY types: fb = 25.78500 GHz

- IEEE 802.3cd-2018 PHY types: fb = 26.5650 GHz

- IEEE P802.3ck Task Force PHY types: fb = 53.12500 GHz

- Frequency spacing: 5 MHz or less

- Intermediate Frequency Bandwidth (IFBW) = 10 KHz or lower

- VNA settings for collected touchstone files need to be applied uniformly to all files per victim lane

### 6.4 Running Matlab Script

When all necessary touchstone files have been collected, the Matlab script is ready to be run. Each COM/ERL script has four input variables:

com\_ieee8023\_93a(config\_file, num\_fext, num\_next, [<s4p files>])

- ► config\_file: This parameter value is a string with the full file path of the xls configuration file.

- num\_fext: This parameter is an integer, specific to the number of far-end crosstalk aggressors associated with the interface being tested.

- num\_next: This parameter is an integer, specific to the number of near-end crosstalk aggressors associated with the interface being tested.

- <s4p\_files>: This parameter is a Matlab structure of touchstone filenames.

If the variables are not supplied by the user, the program will ask for each of them interactively.

When the above input variables are accurately submitted, the Matlab functions will begin processing the touchstone files collected.

| HOME PLOTS                                                                                                                                                                                                                                                                                              | APPS                                             | 🖥 / ħ ti 5 c 🗗 🕐 오 | Search Docur | mentation | 🔎 🜲 🛛 Sign In     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--------------------|--------------|-----------|-------------------|

| < 🔶 🔁 🔂 💭 📙 🕨 C: 🕨 User                                                                                                                                                                                                                                                                                 | S Crutz > Documents > MATLAB                     |                    |              |           | <b>▼</b> <i>P</i> |

| Current Folder 💿                                                                                                                                                                                                                                                                                        | Command Window                                   |                    |              | Workspace |                   |

| 🗋 Name 🔻                                                                                                                                                                                                                                                                                                | New to MATLAB? See resources for Getting Started | <u>1</u> .         | ×            | Name 🔺    | Value             |

| Through.s4p        NEXT4.s4p        NEXT3.s4p        NEXT2.s4p        NEXT2.s4p        FEXT3.s4p        FEXT3.s4p        FEXT3.s4p        FEXT3.s4p        FEXT3.s4p        FEXT3.s4p        FEXT3.s4p        FEXT3.s4p        FEXT1.s4p        Gorn(j.com.jeee8023_93a=100        & com.jeee8023_93a.m | . ∲ >> com_ieee8023_93a                          |                    |              |           |                   |

| Details 🛛 🗸                                                                                                                                                                                                                                                                                             |                                                  |                    |              |           |                   |

|                                                                                                                                                                                                                                                                                                         |                                                  |                    |              | ٢         | >                 |

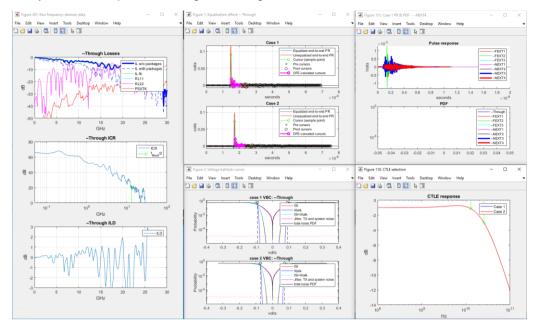

Many informative plots and diagrams are generated.

The conformance COM and ERL values are presented in a text box, as shown below. Values  $\geq$ 3.0 dB are passing (presented with a green text box), and values <3.0 are failing (presented with a red text box).

| COM results                                                                                                | _ | × |

|------------------------------------------------------------------------------------------------------------|---|---|

| Case 1: z_p=(12, 12, 12, 12) (TX, RX, NEXT, FEXT):<br>Case 2: z_p=(30, 30, 12, 30) (TX, RX, NEXT, FEXT):   |   |   |

| ок                                                                                                         |   |   |

| COM results                                                                                                | _ | × |

| Case 1: z_p=(12, 12, 12, 12) (TX, RX, NEXT, FEXT)::<br>Case 2: z_p=(30, 30, 12, 30) (TX, RX, NEXT, FEXT):: |   |   |

| ок                                                                                                         |   |   |

The two 'cases' listed in the COM result box are indicative of an assumed frontend package length in the Host transmit and receive paths. At the time of creating this MOI all of the PHY types that include COM as a conformance metric used the same package length values, "Case 1" refers to a Host TX trace length of 12 mm, RX trace length of 12 mm, and FEXT trace length of 12 mm. "Case 2" refers to a Host TX trace length of 30 mm, RX trace length of 30 mm, NEXT trace length of 12 mm, and FEXT trace length of 12 mm, and FEXT trace length of 30 mm.

# 7 Recommended VNA Port Mapping

## 7.1 Introduction

|   | Measurement | Receiver<br>Under<br>Test |    | jical | Aggressor | VN<br>Log<br>Por | jical | Export Name              |

|---|-------------|---------------------------|----|-------|-----------|------------------|-------|--------------------------|

| 1 | THRU        | RX1A                      | L1 | 1, 3  | TX1B      | L2               | 2, 4  | THRU_L1_RX1A_L2_TX1B.s4p |

| 2 | NEXT        | RX1A                      | L1 | 1, 3  | TX1A      | L2               | 2, 4  | NEXT_L1_RX1A_L2_TX1A.s4p |

| 3 | THRU        | RX1B                      | L1 | 1, 3  | TX1A      | L2               | 2, 4  | THRU_L1_RX1B_L2_TX1A.s4p |

| 4 | NEXT        | RX1B                      | L1 | 1, 3  | TX1B      | L2               | 2, 4  | NEXT_L1_RX1B_L2_TX1B.s4p |

PHY with 1x Transmit lane (CR/KR & CR1/KR1 or equivalent) s4p file names

PHY with 2x Transmit Lanes (CR2/KR2 or equivalent) s4p file names

|    | Measurement | Receiver<br>Under<br>Test |    | gical | Aggressor | VN<br>Log<br>Por | jical | Export Name              |

|----|-------------|---------------------------|----|-------|-----------|------------------|-------|--------------------------|

| 1  | THRU        | RX1A                      | L1 | 1, 3  | TX1B      | L2               | 2, 4  | THRU_L1_RX1A_L2_TX1B.s4p |

| 2  | NEXT        | RX1A                      | L1 | 1, 3  | TX1A      | L2               | 2, 4  | NEXT_L1_RX1A_L2_TX1A.s4p |

| 3  | NEXT        | RX1A                      | L1 | 1, 3  | TX2A      | L2               | 2, 4  | NEXT_L1_RX1A_L2_TX2A.s4p |

| 4  | FEXT        | RX1A                      | L1 | 1, 3  | TX2B      | L2               | 2, 4  | FEXT_L1_RX1A_L2_TX2B.s4p |

| 5  | THRU        | RX2A                      | L1 | 1, 3  | TX2B      | L2               | 2, 4  | THRU_L1_RX2A_L2_TX2B.s4p |

| 6  | NEXT        | RX2A                      | L1 | 1, 3  | TX1A      | L2               | 2, 4  | NEXT_L1_RX2A_L2_TX1A.s4p |

| 7  | NEXT        | RX2A                      | L1 | 1, 3  | TX2A      | L2               | 2, 4  | NEXT_L1_RX2A_L2_TX2A.s4p |

| 8  | FEXT        | RX2A                      | L1 | 1, 3  | TX1B      | L2               | 2, 4  | FEXT_L1_RX2A_L2_TX1B.s4p |

| 9  | THRU        | RX1B                      | L1 | 1, 3  | TX1A      | L2               | 2, 4  | THRU_L1_RX1B_L2_TX1A.s4p |

| 10 | NEXT        | RX1B                      | L1 | 1, 3  | TX1B      | L2               | 2, 4  | NEXT_L1_RX1B_L2_TX1B.s4p |

| 11 | NEXT        | RX1B                      | L1 | 1, 3  | TX2B      | L2               | 2, 4  | NEXT_L1_RX1B_L2_TX2B.s4p |

| 12 | FEXT        | RX1B                      | L1 | 1, 3  | TX2A      | L2               | 2, 4  | FEXT_L1_RX1B_L2_TX2A.s4p |

| 13 | THRU        | RX2B                      | L1 | 1, 3  | TX2A      | L2               | 2, 4  | THRU_L1_RX2B_L2_TX2A.s4p |

| 14 | NEXT        | RX2B                      | L1 | 1, 3  | TX1B      | L2               | 2, 4  | NEXT_L1_RX2B_L2_TX1B.s4p |

| 15 | NEXT        | RX2B                      | L1 | 1, 3  | TX2B      | L2               | 2, 4  | NEXT_L1_RX2B_L2_TX2B.s4p |

|  | 16 FEXT | RX2B | L1 1, 3 TX1A | L2 2, 4 FEXT_L1_RX2B_L2_TX1A.s4p |

|--|---------|------|--------------|----------------------------------|

|--|---------|------|--------------|----------------------------------|

|    | Measurement | Receiver<br>Under<br>Test |    | gical | Aggressor | VN<br>Log<br>Por | jical | Export Name                           |

|----|-------------|---------------------------|----|-------|-----------|------------------|-------|---------------------------------------|

| 1  | THRU        | RX1A                      | L1 | 1, 3  | TX1B      | L2               | 2, 4  | THRU_L1_RX1A_L2_TX1B.s4p              |

| 2  | NEXT        | RX1A                      |    | 1, 3  | TX1A      |                  |       | NEXT_L1_RX1A_L2_TX1A.s4p              |

| 3  | NEXT        | RX1A                      |    | 1, 3  | TX2A      |                  |       | NEXT_L1_RX1A_L2_TX2A.s4p              |

| 4  | NEXT        | RX1A                      |    | 1, 3  | ТХЗА      |                  |       | NEXT_L1_RX1A_L2_TX3A.s4p              |

| 5  | NEXT        | RX1A                      |    | 1, 3  | TX4A      |                  |       | NEXT_L1_RX1A_L2_TX4A.s4p              |

|    |             |                           |    |       |           |                  |       | · · · · · · · · · · · · · · · · · · · |

| 6  | FEXT        | RX1A                      |    | 1, 3  | TX2B      |                  |       | FEXT_L1_RX1A_L2_TX2B.s4p              |

| 7  | FEXT        | RX1A                      | L1 | 1, 3  | ТХЗВ      | L2               | 2, 4  | FEXT_L1_RX1A_L2_TX3B.s4p              |

| 8  | FEXT        | RX1A                      | L1 | 1, 3  | TX4B      | L2               | 2, 4  | FEXT_L1_RX1A_L2_TX4B.s4p              |

| 9  | THRU        | RX2A                      | L1 | 1, 3  | TX2B      | L2               | 2, 4  | THRU_L1_RX2A_L2_TX2B.s4p              |

| 10 | NEXT        | RX2A                      | L1 | 1, 3  | TX1A      | L2               | 2, 4  | NEXT_L1_RX2A_L2_TX1A.s4p              |

| 11 | NEXT        | RX2A                      | L1 | 1, 3  | TX2A      | L2               | 2, 4  | NEXT_L1_RX2A_L2_TX2A.s4p              |

| 12 | NEXT        | RX2A                      | L1 | 1, 3  | ТХЗА      | L2               | 2, 4  | NEXT_L1_RX2A_L2_TX3A.s4p              |

| 13 | NEXT        | RX2A                      | L1 | 1, 3  | TX4A      | L2               | 2, 4  | NEXT_L1_RX2A_L2_TX4A.s4p              |

| 14 | FEXT        | RX2A                      | L1 | 1, 3  | TX1B      | L2               | 2, 4  | FEXT_L1_RX2A_L2_TX1B.s4p              |

| 15 | FEXT        | RX2A                      | L1 | 1, 3  | ТХ3В      | L2               | 2, 4  | FEXT_L1_RX2A_L2_TX3B.s4p              |

| 16 | FEXT        | RX2A                      | L1 | 1, 3  | TX4B      | L2               | 2, 4  | FEXT_L1_RX2A_L2_TX4B.s4p              |

| 17 | THRU        | RX3A                      | L1 | 1, 3  | ТХЗВ      | L2               | 2, 4  | THRU_L1_RX3A_L2_TX3B.s4p              |

| 18 | NEXT        | RX3A                      | L1 | 1, 3  | TX1A      | L2               | 2, 4  | NEXT_L1_RX3A_L2_TX1A.s4p              |

| 19 | NEXT        | RX3A                      | L1 | 1, 3  | TX2A      | L2               | 2, 4  | NEXT_L1_RX3A_L2_TX2A.s4p              |

| 20 | NEXT        | RX3A                      | L1 | 1, 3  | ТХЗА      | L2               | 2, 4  | NEXT_L1_RX3A_L2_TX3A.s4p              |

| 21 | NEXT        | RX3A                      | L1 | 1, 3  | TX4A      | L2               | 2, 4  | NEXT_L1_RX3A_L2_TX4A.s4p              |

| 22 | FEXT        | RX3A                      | L1 | 1, 3  | TX1B      | L2               | 2, 4  | FEXT_L1_RX3A_L2_TX1B.s4p              |

| 23 | FEXT        | RX3A                      | L1 | 1, 3  | TX2B      | L2               | 2, 4  | FEXT_L1_RX3A_L2_TX2B.s4p              |

| 24 | FEXT        | RX3A                      | L1 | 1, 3  | TX4B      | L2               | 2, 4  | FEXT_L1_RX3A_L2_TX4B.s4p              |

| 25 | THRU        | RX4A                      | L1 | 1, 3  | TX4B      | L2               | 2, 4  | THRU_L1_RX4A_L2_TX4B.s4p              |

PHY with 4x Transmit Lanes (CR4/KR4 or equivalent) s4p file names

| 26    NEXT    RX4A    L1    1,3    TX1A    L2    2,4    NEXT_L1_RX4A_L2_TX1A_s44      27    NEXT    RX4A    L1    1,3    TX2A    L2    2,4    NEXT_L1_RX4A_L2_TX3A_s44      28    NEXT    RX4A    L1    1,3    TX3A    L2    2,4    NEXT_L1_RX4A_L2_TX4A_s44      30    FEXT    RX4A    L1    1,3    TX1B    L2    2,4    NEXT_L1_RX4A_L2_TX1B_s44      31    FEXT    RX4A    L1    1,3    TX2B    L2    2,4    FEXT_L1_RX4A_L2_TX3B_s44      32    FEXT    RX4A    L1    1,3    TX1B    L2    2,4    FEXT_L1_RX4A_L2_TX3B_s44      33    THRU    RX1B    L1    1,3    TX1A    L2    2,4    NEXT_L1_RX1B_L2_TX3B_s44      34    NEXT    RX1B    L1    1,3    TX1B    L2    2,4    NEXT_L1_RX1B_L2_TX3B_s44      35    NEXT    RX1B    L1    1,3    TX2B    L2    2,4    NEXT_L1_RX1B_L2_TX3B_s44      36    NEXT    RX1B    L1    1,3    TX2A    L             | 26 |      | RX4A | 11 | 1 2  | TX1A | 12 | 2 4  | NEYT 11 BY4A 12 TY1A s4p |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|------|------|----|------|------|----|------|--------------------------|

| 28    NEXT    RX4A    L1    1, 3    TX3A    L2    2, 4    NEXT_L1_RX4A_L2_TX4A_s4;      29    NEXT    RX4A    L1    1, 3    TX4A    L2    2, 4    NEXT_L1_RX4A_L2_TX4A_s4;      30    FEXT    RX4A    L1    1, 3    TX1B    L2    2, 4    NEXT_L1_RX4A_L2_TX4B_s4;      31    FEXT    RX4A    L1    1, 3    TX2B    L2    2, 4    FEXT_L1_RX4A_L2_TX3B_s4;      32    FEXT    RX4A    L1    1, 3    TX1B    L2    2, 4    FEXT_L1_RX4A_L2_TX3B_s4;      33    THRU    RX1B    L1    1, 3    TX1A    L2    2, 4    FEXT_L1_RX4A_L2_TX3B_s4;      34    NEXT    RX1B    L1    1, 3    TX1B    L2    2, 4    NEXT_L1_RX1B_L2_TX3B_s4;      36    NEXT    RX1B    L1    1, 3    TX2B    L2    2, 4    NEXT_L1_RX1B_L2_TX2B_s4;      36    NEXT    RX1B    L1    1, 3    TX2B    L2    2, 4    NEXT_L1_RX1B_L2_TX2B_s4;      37    NEXT    RX1B    L1    1, 3    TX |    |      |      |    |      |      |    |      |                          |

| 29    NEXT    RX4A    L1    1, 3    TX4A    L2    2, 4    NEXT_L1_RX4A_L2_TX4A.s4;      30    FEXT    RX4A    L1    1, 3    TX1B    L2    2, 4    FEXT_L1_RX4A_L2_TX4B.s4;      31    FEXT    RX4A    L1    1, 3    TX2B    L2    2, 4    FEXT_L1_RX4A_L2_TX4B.s4;      32    FEXT    RX4A    L1    1, 3    TX3B    L2    2, 4    FEXT_L1_RX4A_L2_TX4B.s4;      33    THRU    RX1B    L1    1, 3    TX1A    L2    2, 4    FEXT_L1_RX4A_L2_TX1B.s4;      34    NEXT    RX1B    L1    1, 3    TX1A    L2    2, 4    NEXT_L1_RX1B_L2_TX1B.s4;      35    NEXT    RX1B    L1    1, 3    TX2B    L2    2, 4    NEXT_L1_RX1B_L2_TX2B.s4;      36    NEXT    RX1B    L1    1, 3    TX2B    L2    2, 4    NEXT_L1_RX1B_L2_TX2B.s4;      37    NEXT    RX1B    L1    1, 3    TX4A    L2    2, 4    NEXT_L1_RX1B_L2_TX4B.s4;      36    NEXT    RX1B    L1    1, 3    TX | 27 | NEXT | RX4A | L1 | 1, 3 | TX2A | L2 | 2, 4 | NEXT_L1_RX4A_L2_TX2A.s4p |

| 30    FEXT    RX4A    L1    1,3    TX1B    L2    2,4    FEXT_L1_RX4A_L2_TX1B.s4f      31    FEXT    RX4A    L1    1,3    TX2B    L2    2,4    FEXT_L1_RX4A_L2_TX2B.s4f      32    FEXT    RX4A    L1    1,3    TX3B    L2    2,4    FEXT_L1_RX4A_L2_TX3B.s4f      33    THRU    RX1B    L1    1,3    TX1A    L2    2,4    FEXT_L1_RX1B_L2_TX1A.s4f      34    NEXT    RX1B    L1    1,3    TX1B    L2    2,4    NEXT_L1_RX1B_L2_TX1B.s4f      36    NEXT    RX1B    L1    1,3    TX2B    L2    2,4    NEXT_L1_RX1B_L2_TX2B.s4f      36    NEXT    RX1B    L1    1,3    TX4B    L2    2,4    NEXT_L1_RX1B_L2_TX4B.s4f      37    NEXT    RX1B    L1    1,3    TX4B    L2    2,4    NEXT_L1_RX1B_L2_TX4B.s4f      38    FEXT    RX1B    L1    1,3    TX4A    L2    2,4    FEXT_L1_RX1B_L2_TX4B.s4f      40    FEXT    RX1B    L1    1,3    TX4A    L             | 28 | NEXT | RX4A | L1 | 1, 3 | ТХЗА | L2 | 2, 4 | NEXT_L1_RX4A_L2_TX3A.s4p |

| 31    FEXT    RX4A    L1    1,3    TX2B    L2    2,4    FEXT_L1_RX4A_L2_TX2B.s4f      32    FEXT    RX4A    L1    1,3    TX3B    L2    2,4    FEXT_L1_RX4A_L2_TX3B.s4f      33    THRU    RX1B    L1    1,3    TX1A    L2    2,4    FEXT_L1_RX4A_L2_TX3B.s4f      34    NEXT    RX1B    L1    1,3    TX1B    L2    2,4    HRU_L1_RX1B_L2_TX1B.s4f      35    NEXT    RX1B    L1    1,3    TX2B    L2    2,4    NEXT_L1_RX1B_L2_TX3B.s4f      36    NEXT    RX1B    L1    1,3    TX2B    L2    2,4    NEXT_L1_RX1B_L2_TX3B.s4f      36    NEXT    RX1B    L1    1,3    TX2B    L2    2,4    NEXT_L1_RX1B_L2_TX4B.s4f      36    NEXT    RX1B    L1    1,3    TX2A    L2    2,4    FEXT_L1_RX1B_L2_TX4B.s4f      37    NEXT    RX1B    L1    1,3    TX2A    L2    2,4    FEXT_L1_RX1B_L2_TX4A.s4f      40    FEXT    RX1B    L1    1,3    TX4A    L2             | 29 | NEXT | RX4A | L1 | 1, 3 | TX4A | L2 | 2, 4 | NEXT_L1_RX4A_L2_TX4A.s4p |

| 32    FEXT    RX4A    L1    1, 3    TX3B    L2    2, 4    FEXT_L1_RX4A_L2_TX3B.s4f      33    THRU    RX1B    L1    1, 3    TX1A    L2    2, 4    THRU_L1_RX1B_L2_TX1B.s4f      34    NEXT    RX1B    L1    1, 3    TX1A    L2    2, 4    NEXT_L1_RX1B_L2_TX1B.s4f      35    NEXT    RX1B    L1    1, 3    TX2B    L2    2, 4    NEXT_L1_RX1B_L2_TX2B.s4f      36    NEXT    RX1B    L1    1, 3    TX3B    L2    2, 4    NEXT_L1_RX1B_L2_TX2B.s4f      37    NEXT    RX1B    L1    1, 3    TX4B    L2    2, 4    NEXT_L1_RX1B_L2_TX2B.s4f      38    FEXT    RX1B    L1    1, 3    TX2A    L2    2, 4    FEXT_L1_RX1B_L2_TX2A.s4f      40    FEXT    RX1B    L1    1, 3    TX4A    L2    2, 4    FEXT_L1_RX1B_L2_TX4A.s4f      41    THRU    RX2B    L1    1, 3    TX4A    L2    2, 4    FEXT_L1_RX1B_L2_TX4A.s4f      42    NEXT    RX2B    L1    1, 3    TX | 30 | FEXT | RX4A | L1 | 1, 3 | TX1B | L2 | 2, 4 | FEXT_L1_RX4A_L2_TX1B.s4p |

| 33    THRU    RX1B    L1    1, 3    TX1A    L2    2, 4    THRU_L1_RX1B_L2_TX1A,s4      34    NEXT    RX1B    L1    1, 3    TX1B    L2    2, 4    NEXT_L1_RX1B_L2_TX1A,s4      35    NEXT    RX1B    L1    1, 3    TX2B    L2    2, 4    NEXT_L1_RX1B_L2_TX2B,s4¢      36    NEXT    RX1B    L1    1, 3    TX2B    L2    2, 4    NEXT_L1_RX1B_L2_TX2B,s4¢      36    NEXT    RX1B    L1    1, 3    TX2B    L2    2, 4    NEXT_L1_RX1B_L2_TX2B,s4¢      37    NEXT    RX1B    L1    1, 3    TX2A    L2    2, 4    NEXT_L1_RX1B_L2_TX2A,s4¢      38    FEXT    RX1B    L1    1, 3    TX2A    L2    2, 4    FEXT_L1_RX1B_L2_TX3A,s4¢      40    FEXT    RX1B    L1    1, 3    TX2A    L2    2, 4    FEXT_L1_RX1B_L2_TX4A,s4¢      41    THRU    RX2B    L1    1, 3    TX2A    L2    2, 4    FEXT_L1_RX1B_L2_TX4A,s4¢      42    NEXT    RX2B    L1    1, 3    TX2A | 31 | FEXT | RX4A | L1 | 1, 3 | TX2B | L2 | 2, 4 | FEXT_L1_RX4A_L2_TX2B.s4p |

| 34    NEXT    RX1B    L1    1, 3    TX1B    L2    2, 4    NEXT_L1_RX1B_L2_TX1B_s4f      35    NEXT    RX1B    L1    1, 3    TX2B    L2    2, 4    NEXT_L1_RX1B_L2_TX2B_s4f      36    NEXT    RX1B    L1    1, 3    TX2B    L2    2, 4    NEXT_L1_RX1B_L2_TX2B_s4f      37    NEXT    RX1B    L1    1, 3    TX2B    L2    2, 4    NEXT_L1_RX1B_L2_TX3B_s4f      38    FEXT    RX1B    L1    1, 3    TX2A    L2    2, 4    NEXT_L1_RX1B_L2_TX4B_s4f      38    FEXT    RX1B    L1    1, 3    TX2A    L2    2, 4    FEXT_L1_RX1B_L2_TX4A_s4f      40    FEXT    RX1B    L1    1, 3    TX2A    L2    2, 4    FEXT_L1_RX1B_L2_TX4A_s4f      41    THRU    RX2B    L1    1, 3    TX2A    L2    2, 4    FEXT_L1_RX1B_L2_TX4A_s4f      42    NEXT    RX1B    L1    1, 3    TX2A    L2    2, 4    FEXT_L1_RX1B_L2_TX4A_s4f      43    NEXT    RX2B    L1    1, 3    TX | 32 | FEXT | RX4A | L1 | 1, 3 | ТХЗВ | L2 | 2, 4 | FEXT_L1_RX4A_L2_TX3B.s4p |

| 35    NEXT    RX1B    L1    1, 3    TX2B    L2    2, 4    NEXT_L1_RX1B_L2_TX2B.s4f      36    NEXT    RX1B    L1    1, 3    TX3B    L2    2, 4    NEXT_L1_RX1B_L2_TX3B.s4f      37    NEXT    RX1B    L1    1, 3    TX4B    L2    2, 4    NEXT_L1_RX1B_L2_TX3B.s4f      38    FEXT    RX1B    L1    1, 3    TX2A    L2    2, 4    FEXT_L1_RX1B_L2_TX2A.s4f      39    FEXT    RX1B    L1    1, 3    TX2A    L2    2, 4    FEXT_L1_RX1B_L2_TX2A.s4f      40    FEXT    RX1B    L1    1, 3    TX2A    L2    2, 4    FEXT_L1_RX1B_L2_TX2A.s4f      41    THRU    RX2B    L1    1, 3    TX2A    L2    2, 4    FEXT_L1_RX1B_L2_TX2A.s4f      42    NEXT    RX2B    L1    1, 3    TX2A    L2    2, 4    FEXT_L1_RX1B_L2_TX2A.s4f      43    NEXT    RX2B    L1    1, 3    TX2A    L2    2, 4    NEXT_L1_RX2B_L2_TX1B.s4f      43    NEXT    RX2B    L1    1, 3    TX | 33 | THRU | RX1B | L1 | 1, 3 | TX1A | L2 | 2, 4 | THRU_L1_RX1B_L2_TX1A.s4p |

| 36    NEXT    RX1B    L1    1, 3    TX3B    L2    2, 4    NEXT_L1_RX1B_L2_TX3B.s4f      37    NEXT    RX1B    L1    1, 3    TX4B    L2    2, 4    NEXT_L1_RX1B_L2_TX4B.s4f      38    FEXT    RX1B    L1    1, 3    TX4B    L2    2, 4    FEXT_L1_RX1B_L2_TX4B.s4f      39    FEXT    RX1B    L1    1, 3    TX3A    L2    2, 4    FEXT_L1_RX1B_L2_TX4A.s4f      40    FEXT    RX1B    L1    1, 3    TX3A    L2    2, 4    FEXT_L1_RX1B_L2_TX4A.s4f      41    THRU    RX2B    L1    1, 3    TX2A    L2    2, 4    FEXT_L1_RX1B_L2_TX4A.s4f      41    THRU    RX2B    L1    1, 3    TX2A    L2    2, 4    FEXT_L1_RX1B_L2_TX4A.s4f      42    NEXT    RX2B    L1    1, 3    TX2A    L2    2, 4    FEXT_L1_RX2B_L2_TX4A.s4f      43    NEXT    RX2B    L1    1, 3    TX2B    L2    2, 4    NEXT_L1_RX2B_L2_TX2B.s4f      44    NEXT    RX2B    L1    1, 3    TX | 34 | NEXT | RX1B | L1 | 1, 3 | TX1B | L2 | 2, 4 | NEXT_L1_RX1B_L2_TX1B.s4p |

| 37    NEXT    RX1B    L1    1, 3    TX4B    L2    2, 4    NEXT_L1_RX1B_L2_TX4B.s4f      38    FEXT    RX1B    L1    1, 3    TX2A    L2    2, 4    FEXT_L1_RX1B_L2_TX2A.s4f      39    FEXT    RX1B    L1    1, 3    TX3A    L2    2, 4    FEXT_L1_RX1B_L2_TX3A.s4f      40    FEXT    RX1B    L1    1, 3    TX4A    L2    2, 4    FEXT_L1_RX1B_L2_TX4A.s4f      41    THRU    RX2B    L1    1, 3    TX4A    L2    2, 4    FEXT_L1_RX1B_L2_TX4A.s4f      42    NEXT    RX2B    L1    1, 3    TX4A    L2    2, 4    FEXT_L1_RX2B_L2_TX2A.s4f      43    NEXT    RX2B    L1    1, 3    TX1B    L2    2, 4    NEXT_L1_RX2B_L2_TX2B.s4f      44    NEXT    RX2B    L1    1, 3    TX3B    L2    2, 4    NEXT_L1_RX2B_L2_TX3B.s4f      45    NEXT    RX2B    L1    1, 3    TX3B    L2    2, 4    NEXT_L1_RX2B_L2_TX3B.s4f      46    FEXT    RX2B    L1    1, 3    TX | 35 | NEXT | RX1B | L1 | 1, 3 | TX2B | L2 | 2, 4 | NEXT_L1_RX1B_L2_TX2B.s4p |

| 38    FEXT    RX1B    L1    1, 3    TX2A    L2    2, 4    FEXT_L1_RX1B_L2_TX2A.s4p      39    FEXT    RX1B    L1    1, 3    TX3A    L2    2, 4    FEXT_L1_RX1B_L2_TX3A.s4p      40    FEXT    RX1B    L1    1, 3    TX3A    L2    2, 4    FEXT_L1_RX1B_L2_TX3A.s4p      41    THRU    RX2B    L1    1, 3    TX4A    L2    2, 4    FEXT_L1_RX1B_L2_TX4A.s4p      42    NEXT    RX2B    L1    1, 3    TX1B    L2    2, 4    THRU_L1_RX2B_L2_TX2A.s4p      43    NEXT    RX2B    L1    1, 3    TX1B    L2    2, 4    NEXT_L1_RX2B_L2_TX2B.s4p      43    NEXT    RX2B    L1    1, 3    TX3B    L2    2, 4    NEXT_L1_RX2B_L2_TX3B.s4p      44    NEXT    RX2B    L1    1, 3    TX3B    L2    2, 4    NEXT_L1_RX2B_L2_TX3B.s4p      45    NEXT    RX2B    L1    1, 3    TX4B    L2    2, 4    FEXT_L1_RX2B_L2_TX3A.s4p      46    FEXT    RX2B    L1    1, 3    TX | 36 | NEXT | RX1B | L1 | 1, 3 | ТХЗВ | L2 | 2, 4 | NEXT_L1_RX1B_L2_TX3B.s4p |

| 39    FEXT    RX1B    L1    1, 3    TX3A    L2    2, 4    FEXT_L1_RX1B_L2_TX3A.s4p      40    FEXT    RX1B    L1    1, 3    TX4A    L2    2, 4    FEXT_L1_RX1B_L2_TX4A.s4p      41    THRU    RX2B    L1    1, 3    TX2A    L2    2, 4    FEXT_L1_RX1B_L2_TX4A.s4p      42    NEXT    RX2B    L1    1, 3    TX2A    L2    2, 4    THRU_L1_RX2B_L2_TX2A.s4p      43    NEXT    RX2B    L1    1, 3    TX2B    L2    2, 4    NEXT_L1_RX2B_L2_TX2B.s4p      44    NEXT    RX2B    L1    1, 3    TX3B    L2    2, 4    NEXT_L1_RX2B_L2_TX3B.s4p      44    NEXT    RX2B    L1    1, 3    TX3B    L2    2, 4    NEXT_L1_RX2B_L2_TX3B.s4p      45    NEXT    RX2B    L1    1, 3    TX4B    L2    2, 4    NEXT_L1_RX2B_L2_TX3B.s4p      46    FEXT    RX2B    L1    1, 3    TX1A    L2    2, 4    FEXT_L1_RX2B_L2_TX3A.s4p      47    FEXT    RX2B    L1    1, 3    TX | 37 | NEXT | RX1B | L1 | 1, 3 | TX4B | L2 | 2, 4 | NEXT_L1_RX1B_L2_TX4B.s4p |

| 40    FEXT    RX1B    L1    1,3    TX4A    L2    2,4    FEXT_L1_RX1B_L2_TX4A.s4p      41    THRU    RX2B    L1    1,3    TX2A    L2    2,4    THRU_L1_RX2B_L2_TX2A.s4p      42    NEXT    RX2B    L1    1,3    TX1B    L2    2,4    THRU_L1_RX2B_L2_TX2A.s4p      43    NEXT    RX2B    L1    1,3    TX1B    L2    2,4    NEXT_L1_RX2B_L2_TX2B.s4p      44    NEXT    RX2B    L1    1,3    TX3B    L2    2,4    NEXT_L1_RX2B_L2_TX3B.s4p      44    NEXT    RX2B    L1    1,3    TX3B    L2    2,4    NEXT_L1_RX2B_L2_TX3B.s4p      45    NEXT    RX2B    L1    1,3    TX4B    L2    2,4    NEXT_L1_RX2B_L2_TX4B.s4p      46    FEXT    RX2B    L1    1,3    TX1A    L2    2,4    NEXT_L1_RX2B_L2_TX4B.s4p      47    FEXT    RX2B    L1    1,3    TX1A    L2    2,4    FEXT_L1_RX2B_L2_TX4A.s4p      48    FEXT    RX2B    L1    1,3    TX3A    L             | 38 | FEXT | RX1B | L1 | 1, 3 | TX2A | L2 | 2, 4 | FEXT_L1_RX1B_L2_TX2A.s4p |

| 41    THRU    RX2B    L1    1, 3    TX2A    L2    2, 4    THRU_L1_RX2B_L2_TX2A.s4      42    NEXT    RX2B    L1    1, 3    TX1B    L2    2, 4    NEXT_L1_RX2B_L2_TX1B.s4      43    NEXT    RX2B    L1    1, 3    TX1B    L2    2, 4    NEXT_L1_RX2B_L2_TX2B.s4      44    NEXT    RX2B    L1    1, 3    TX3B    L2    2, 4    NEXT_L1_RX2B_L2_TX3B.s4      44    NEXT    RX2B    L1    1, 3    TX3B    L2    2, 4    NEXT_L1_RX2B_L2_TX3B.s4      45    NEXT    RX2B    L1    1, 3    TX4B    L2    2, 4    NEXT_L1_RX2B_L2_TX4B.s4      46    FEXT    RX2B    L1    1, 3    TX1A    L2    2, 4    FEXT_L1_RX2B_L2_TX4B.s4      47    FEXT    RX2B    L1    1, 3    TX3A    L2    2, 4    FEXT_L1_RX2B_L2_TX3A.s4      48    FEXT    RX2B    L1    1, 3    TX4A    L2    2, 4    FEXT_L1_RX3B_L2_TX3A.s4      49    THRU    RX3B    L1    1, 3    TX1B        | 39 | FEXT | RX1B | L1 | 1, 3 | ТХЗА | L2 | 2, 4 | FEXT_L1_RX1B_L2_TX3A.s4p |

| 42    NEXT    RX2B    L1    1,3    TX1B    L2    2,4    NEXT_L1_RX2B_L2_TX1B.s4g      43    NEXT    RX2B    L1    1,3    TX2B    L2    2,4    NEXT_L1_RX2B_L2_TX2B.s4g      44    NEXT    RX2B    L1    1,3    TX3B    L2    2,4    NEXT_L1_RX2B_L2_TX3B.s4g      45    NEXT    RX2B    L1    1,3    TX4B    L2    2,4    NEXT_L1_RX2B_L2_TX3B.s4g      46    FEXT    RX2B    L1    1,3    TX1A    L2    2,4    NEXT_L1_RX2B_L2_TX4B.s4g      47    FEXT    RX2B    L1    1,3    TX1A    L2    2,4    FEXT_L1_RX2B_L2_TX1A.s4g      48    FEXT    RX2B    L1    1,3    TX3A    L2    2,4    FEXT_L1_RX2B_L2_TX3A.s4g      49    THRU    RX3B    L1    1,3    TX3A    L2    2,4    FEXT_L1_RX3B_L2_TX3A.s4g      50    NEXT    RX3B    L1    1,3    TX1A    L2    2,4    NEXT_L1_RX3B_L2_TX3A.s4g      51    NEXT    RX3B    L1    1,3    TX3A    L             | 40 | FEXT | RX1B | L1 | 1, 3 | TX4A | L2 | 2, 4 | FEXT_L1_RX1B_L2_TX4A.s4p |

| 43    NEXT    RX2B    L1    1, 3    TX2B    L2    2, 4    NEXT_L1_RX2B_L2_TX2B.s4g      44    NEXT    RX2B    L1    1, 3    TX3B    L2    2, 4    NEXT_L1_RX2B_L2_TX3B.s4g      45    NEXT    RX2B    L1    1, 3    TX4B    L2    2, 4    NEXT_L1_RX2B_L2_TX3B.s4g      46    FEXT    RX2B    L1    1, 3    TX1A    L2    2, 4    NEXT_L1_RX2B_L2_TX1A.s4g      47    FEXT    RX2B    L1    1, 3    TX3A    L2    2, 4    FEXT_L1_RX2B_L2_TX1A.s4g      48    FEXT    RX2B    L1    1, 3    TX4A    L2    2, 4    FEXT_L1_RX2B_L2_TX3A.s4g      49    THRU    RX3B    L1    1, 3    TX3A    L2    2, 4    FEXT_L1_RX3B_L2_TX3A.s4g      50    NEXT    RX3B    L1    1, 3    TX1B    L2    2, 4    NEXT_L1_RX3B_L2_TX3B.s4g      51    NEXT    RX3B    L1    1, 3    TX2B    L2    2, 4    NEXT_L1_RX3B_L2_TX3B.s4g      52    NEXT    RX3B    L1    1, 3    TX | 41 | THRU | RX2B | L1 | 1, 3 | TX2A | L2 | 2, 4 | THRU_L1_RX2B_L2_TX2A.s4p |

| 44    NEXT    RX2B    L1    1, 3    TX3B    L2    2, 4    NEXT_L1_RX2B_L2_TX3B.s4g      45    NEXT    RX2B    L1    1, 3    TX4B    L2    2, 4    NEXT_L1_RX2B_L2_TX4B.s4g      46    FEXT    RX2B    L1    1, 3    TX1A    L2    2, 4    NEXT_L1_RX2B_L2_TX4B.s4g      47    FEXT    RX2B    L1    1, 3    TX1A    L2    2, 4    FEXT_L1_RX2B_L2_TX1A.s4g      48    FEXT    RX2B    L1    1, 3    TX3A    L2    2, 4    FEXT_L1_RX2B_L2_TX3A.s4g      49    THRU    RX3B    L1    1, 3    TX3A    L2    2, 4    FEXT_L1_RX2B_L2_TX3A.s4g      50    NEXT    RX3B    L1    1, 3    TX3A    L2    2, 4    THRU_L1_RX3B_L2_TX3A.s4g      51    NEXT    RX3B    L1    1, 3    TX1B    L2    2, 4    NEXT_L1_RX3B_L2_TX2B.s4g      52    NEXT    RX3B    L1    1, 3    TX3B    L2    2, 4    NEXT_L1_RX3B_L2_TX3B.s4g                                             | 42 | NEXT | RX2B | L1 | 1, 3 | TX1B | L2 | 2, 4 | NEXT_L1_RX2B_L2_TX1B.s4p |

| 45    NEXT    RX2B    L1    1, 3    TX4B    L2    2, 4    NEXT_L1_RX2B_L2_TX4B.s4g      46    FEXT    RX2B    L1    1, 3    TX1A    L2    2, 4    FEXT_L1_RX2B_L2_TX1A.s4g      47    FEXT    RX2B    L1    1, 3    TX3A    L2    2, 4    FEXT_L1_RX2B_L2_TX1A.s4g      48    FEXT    RX2B    L1    1, 3    TX3A    L2    2, 4    FEXT_L1_RX2B_L2_TX3A.s4g      49    THRU    RX3B    L1    1, 3    TX3A    L2    2, 4    FEXT_L1_RX2B_L2_TX3A.s4g      50    NEXT    RX3B    L1    1, 3    TX1B    L2    2, 4    NEXT_L1_RX3B_L2_TX3A.s4g      51    NEXT    RX3B    L1    1, 3    TX1B    L2    2, 4    NEXT_L1_RX3B_L2_TX2B.s4g      52    NEXT    RX3B    L1    1, 3    TX3B    L2    2, 4    NEXT_L1_RX3B_L2_TX3B.s4g                                                                                                                                     | 43 | NEXT | RX2B | L1 | 1, 3 | TX2B | L2 | 2, 4 | NEXT_L1_RX2B_L2_TX2B.s4p |

| 46    FEXT    RX2B    L1    1, 3    TX1A    L2    2, 4    FEXT_L1_RX2B_L2_TX1A.s4p      47    FEXT    RX2B    L1    1, 3    TX3A    L2    2, 4    FEXT_L1_RX2B_L2_TX3A.s4p      48    FEXT    RX2B    L1    1, 3    TX3A    L2    2, 4    FEXT_L1_RX2B_L2_TX3A.s4p      49    THRU    RX3B    L1    1, 3    TX3A    L2    2, 4    FEXT_L1_RX2B_L2_TX3A.s4p      50    NEXT    RX3B    L1    1, 3    TX1B    L2    2, 4    NEXT_L1_RX3B_L2_TX3A.s4p      51    NEXT    RX3B    L1    1, 3    TX2B    L2    2, 4    NEXT_L1_RX3B_L2_TX3B.s4p      52    NEXT    RX3B    L1    1, 3    TX2B    L2    2, 4    NEXT_L1_RX3B_L2_TX3B.s4p                                                                                                                                                                                                                             | 44 | NEXT | RX2B | L1 | 1, 3 | ТХ3В | L2 | 2, 4 | NEXT_L1_RX2B_L2_TX3B.s4p |

| 47    FEXT    RX2B    L1    1, 3    TX3A    L2    2, 4    FEXT_L1_RX2B_L2_TX3A.s4p      48    FEXT    RX2B    L1    1, 3    TX4A    L2    2, 4    FEXT_L1_RX2B_L2_TX4A.s4p      49    THRU    RX3B    L1    1, 3    TX3A    L2    2, 4    FEXT_L1_RX2B_L2_TX4A.s4p      50    NEXT    RX3B    L1    1, 3    TX1B    L2    2, 4    NEXT_L1_RX3B_L2_TX3A.s4p      51    NEXT    RX3B    L1    1, 3    TX2B    L2    2, 4    NEXT_L1_RX3B_L2_TX1B.s4p      52    NEXT    RX3B    L1    1, 3    TX2B    L2    2, 4    NEXT_L1_RX3B_L2_TX2B.s4p                                                                                                                                                                                                                                                                                                                     | 45 | NEXT | RX2B | L1 | 1, 3 | TX4B | L2 | 2, 4 | NEXT_L1_RX2B_L2_TX4B.s4p |

| 48    FEXT    RX2B    L1    1, 3    TX4A    L2    2, 4    FEXT_L1_RX2B_L2_TX4A.s4p      49    THRU    RX3B    L1    1, 3    TX3A    L2    2, 4    THRU_L1_RX3B_L2_TX3A.s4p      50    NEXT    RX3B    L1    1, 3    TX1B    L2    2, 4    NEXT_L1_RX3B_L2_TX3A.s4p      51    NEXT    RX3B    L1    1, 3    TX2B    L2    2, 4    NEXT_L1_RX3B_L2_TX1B.s4p      52    NEXT    RX3B    L1    1, 3    TX2B    L2    2, 4    NEXT_L1_RX3B_L2_TX2B.s4p                                                                                                                                                                                                                                                                                                                                                                                                             | 46 | FEXT | RX2B | L1 | 1, 3 | TX1A | L2 | 2, 4 | FEXT_L1_RX2B_L2_TX1A.s4p |

| 49    THRU    RX3B    L1    1, 3    TX3A    L2    2, 4    THRU_L1_RX3B_L2_TX3A.s4      50    NEXT    RX3B    L1    1, 3    TX1B    L2    2, 4    NEXT_L1_RX3B_L2_TX1B.s4µ      51    NEXT    RX3B    L1    1, 3    TX2B    L2    2, 4    NEXT_L1_RX3B_L2_TX1B.s4µ      52    NEXT    RX3B    L1    1, 3    TX3B    L2    2, 4    NEXT_L1_RX3B_L2_TX2B.s4µ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 47 | FEXT | RX2B | L1 | 1, 3 | ТХЗА | L2 | 2, 4 | FEXT_L1_RX2B_L2_TX3A.s4p |

| 50    NEXT    RX3B    L1    1, 3    TX1B    L2    2, 4    NEXT_L1_RX3B_L2_TX1B.s4p      51    NEXT    RX3B    L1    1, 3    TX2B    L2    2, 4    NEXT_L1_RX3B_L2_TX2B.s4p      52    NEXT    RX3B    L1    1, 3    TX3B    L2    2, 4    NEXT_L1_RX3B_L2_TX2B.s4p                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 48 | FEXT | RX2B | L1 | 1, 3 | TX4A | L2 | 2, 4 | FEXT_L1_RX2B_L2_TX4A.s4p |

| 51    NEXT    RX3B    L1    1, 3    TX2B    L2    2, 4    NEXT_L1_RX3B_L2_TX2B.s4p      52    NEXT    RX3B    L1    1, 3    TX3B    L2    2, 4    NEXT_L1_RX3B_L2_TX2B.s4p                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 49 | THRU | RX3B | L1 | 1, 3 | ТХЗА | L2 | 2, 4 | THRU_L1_RX3B_L2_TX3A.s4p |

| 52 NEXT RX3B L1 1, 3 TX3B L2 2, 4 NEXT_L1_RX3B_L2_TX3B.s4p                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 50 | NEXT | RX3B | L1 | 1, 3 | TX1B | L2 | 2, 4 | NEXT_L1_RX3B_L2_TX1B.s4p |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 51 | NEXT | RX3B | L1 | 1, 3 | TX2B | L2 | 2, 4 | NEXT_L1_RX3B_L2_TX2B.s4p |